随着芯片规模的增大,关于IC设计流程中的后仿是否必要,有多种声音。认为不必要的理由是:布局布线后的网表,已经可以通过STA保证时序,后仿只不过是确认一遍电路的时序。而且随着电路规模不断增大,仿真工具的仿真速度的提升仍不明显,后仿必然是一个很耗时的步骤,时间代价大而收益不明显。认为有必要的理由是,从公司以往多个项目的经验来看,后仿中也发现了一些问题。而对于有些设计,STA并不能完全覆盖所有的路径。后仿的工作是对后端实现最后的check。以公司现阶段的情况来看,后仿还是必须的。

仿真器是event-driven的,所有的仿真器是在多核CPU面世前设计的,所以通常仿真器在仿真Verilog代码是是单线程的,即使用户提供一个具有并行计算能力的平台,仿真仍然是串行循序进行的。

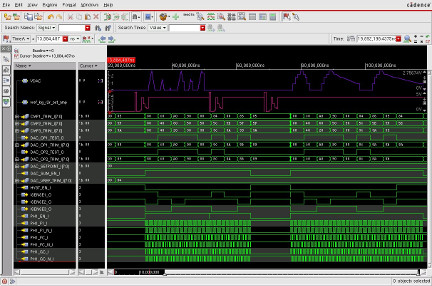

由于后仿真的对象是门级网表+sdf文件,仿真目的主要检查时序约束是否存在问题,时钟树是否合理,电路设计是否有潜在风险,接口设计是否遵循datasheet等。由于后仿的网表规模大,再加上SDF反标的拖累,仿真速度是前仿的几十分之一,要跑完几个典型case就已经极其痛苦,更别提全部的回归。

由于仿真时对单个case来说是使用单个CPU核进行计算的,所以CPU的速度决定了整个仿真的速度。我们在使用Dell Power Edge T620(主频2.6Ghz)进行仿真时,单个case的仿真时间是24小时;使用CIARA超频工作站(主频4.8Ghz),同样的仿真环境需要的时间是11小时;大大提高了仿真的效率。这使得一些带软件的case,如UBOOT等可以使用软仿来进行验证,等两三天毕竟比等一个礼拜要强多了。

在平时验证阶段,仿真的速度决定了验证团队的工作效率,使用超频工作站对于使用者来说只是一个高性能的平台,对验证环境和软件没有额外的要求,可以在使相同的case在一半时间里完成,对验证团队意义重大。